1 自动对花检测方法

平网印花机根据印制的图案不同,通常由几个或十几个花回组成.欲印制精细复杂的花型图案,除网版制作精确外,印花导带行进的每个花回的重复精度也至关重要.一般布动式平网印花机印花导带的驱动方式有两种:一种是依靠液压传动的方式;另一种依靠伺服电机驱动印花导带的方式.无论哪一种驱动方式都存在对花不准的问题.通常,由工人肉眼观察印出的图案有没有出现“错花”、“跑花”现象,若图案有问题,则及时停车对印花设备进行机械调整.

本方案用图像处理的方法实现自动对花检测,较人工观察更加准确和及时.具体实现过程是:当织物通过第一个花回时,需要印花单元在织物上印出检测标记,以对应于花网上的印花图案位置.在印花导带的出布端由CCD摄像头对检测标记进行实时拍摄,然后将拍摄到的检测标记的图像,送人由DM642为核心的图像处理系统进行实时处理,得出检测标记坐标位置.印花起始由人工对机械装置精确定位,因此将第一帧图像中标记的坐标值作为参考值保存下来.当下一帧检测标记的图像摄人以后做同样处理,得到此帧图像中标记的坐标值;处理器将此值与参考值相比较得出坐标位置的偏差,包括水平和垂直两个方向的偏差;再将此偏差转换为导带的偏差量,并判断偏差量是否超过允许的范围(平网印花机对花误差

上位机接到检测系统反馈的信号后进行实时处理.若第一种情况将导带的调整量及时通知给导带驱动器,由导带驱动器对误差做出实时调整以保证每个花回的重复精度;第二种情况,实时报警并给导带驱动器停车信号,印花机停止工作,避免出现更多的次品布.从而完成平网印花机的全自动对花,提高了印花机的印花质量.

2 检测系统硬件电路

检测系统硬件电路采用模块化设计 ,充分利用丁DM642的视频端口和各种外部器件接口.其硬件电路主要由TMS320DM642(DM642)核心处理芯片、视频输入模块、视频输出模块、存储器模块、外围通讯模块以及电源模块等模块组成,如图l所示.

2.1 核心处理芯片DM642

DM642是TI公司在2002年推出的一款专用图像处理芯片.作为本系统的中央处理器,一方面将输入的检测标记的数字图像信号,进行处理后得出检测标记的实时位置;另一方面控制各个模块协调工作,实时与上位机通汛.

DM642的核心频率为600MHz,每个指令周期可并行8条32bit指令,因此速度可达4800MI/s. DM642具有两级缓存结构,第一级包括相互独立的数据缓存区L1D(16k)和程序缓存区LIP(16k),使得程序和数据可以同时读写,进一步提高了CPU的处理速度;第二级缓存L2(256k)存储空间,也可作为 SRAM映射到存储空间.DM642含有64个独立通道的EDMA控制器,负责片内L2与其他外设之间的数据高速传输.

作为专用的图像处理芯片,DM642具有3路双通道视频端口Video port(VP0、VP1、VP2).三路双通道视频端口都是可配置的,支持多种视频标准的输入和显示.在本系统中,只需要一路视频输入口检测织物上的检测标记,一路视频输出口将监测到的图像以及数据输出显示.因此,将VPO配置为视频输入口, VP2配置为视频输出口.

在本系统中,外扩64bit的SDRAM、8bit的FLASH、UART和FPGA,均通过DM642的外部存储器接口(EMIF)进行扩展.DM642的外部存储器接口(EMIF),能够支持64bit、32bit、16bit、8bit的外部器件.EMIF有3个内存控制器,其中SDRAM控制器支持16MB~256MB SDRAM器件,连同可编程的同步与异步控制器控制各种同步和异步存储设备.

DM642具有标准的12C总线接口,利用I2C总线连接驱动设备的控制寄存器,给驱动设备进行在线灵活的配置.此系统的设计就是用I2C总线来配置视频解码器,视频编码器.

2.2 视频输入模块

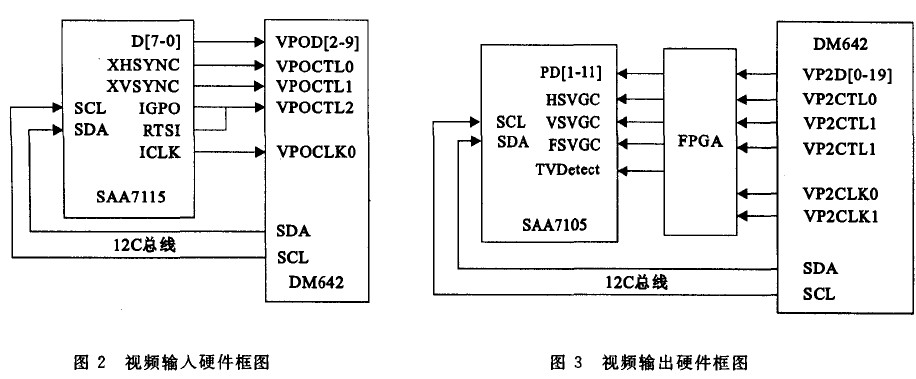

视频输入部分主要由CCD摄像头和视频解码芯片SAA7115组成,如图2所示.

CCD摄像头用来摄取检测标记的图像,将图像转换成标准的视频流.由于检测标记只是用来确定导带的运行位置,不需要彩色摄像头,故采用黑白的CCD摄像头采集图像.因为DSP无法对模拟信号进行处理,所以需要对模拟视频进行A/D转换,SAA7115就是担任此角色.SAA7115具有场消隐期VBI的数据解码,以及高性能的行、场尺度变换功能,并且可通过编程对其进行灵活的配置.在本系统中,SAA7115视频输出格式由DM642通过I2C总线对其配置决定,如设置视频信号输入制式、视频信号通道选择、视频数据输出格式、同步信号插入位置、亮度色度及对比度、同步信号输入开关、视频采集量化启动和关闭等内部寄存器等.输入的视频格式配置为标准的PAL/NTSC制式.由于本系统处理的对象是256 级的灰度图像,故输入图像配置为PAL制式,输出数据编码为标准的y:u:V=4:2:2格式(y代表亮度信息,U(Cb)代表蓝色色差,V(Cr)代表红色色差),以ITUBT656数字码流的形式送入DM642的VP0口进行处理.

2.3 视频输出模块

显示部分主要由显示设备、逻辑器件FPGA和视频编码芯片SAA7l05组成,如图3所示.逻辑器件FPGA用来完成高级功能,以及一些接口的逻辑控制信号.作为视频显示用时可以配置为不同的操作方式,在默认的方式下设置为直接通过视频,连接到SAA7105视频编码器.对于OSD功能, FPGA提供了FIFOs,将视频端口2的数据与FIFOs的数据进行混合.系统中FPGA采用Xilinx XC2S300.此芯片提供连续的编程端口,系统设计时由DM642通过这几个编程端口对FPGA实时编程,以完成不同的配置和操作.

在本系统中,视频编码器SAA7105由DM642通过I2C总线对内部编程寄存器在线设置为PAL制式,将来自FPGA的442编码格式的ITUBT656数字视频流,合成模拟的PAL制式视频信号,送入显示设备显示.

2.4 存储器模块

2.4.1 动态存储器模块(SDRAM) 在系统中需要对图像信号进行实时的存储.一帧PAL制式422编码格式的图像,需要的存储空间为720×576×2=829 440(字节).DM642内部虽然有256k的二级缓存区可以作为SRAM使用,显然还不能满足要求,为此需要进行存储器的外扩.

在本系统中外扩了两块4M×64bit同步动态存储器(SDRAM)MT48LC4M32B2芯片,可以存储可达32帧的图像,这两片SDRAM在DM642存储区中统一编址,映射在DM642的外部存储器CE0空间,首地址为0x80000000.系统工作时,首先将检测标记的图像存储在SDRAM 中,需要处理时通过DMA通道从SDRAM 中,分块读入DM642的内部缓存区中,在处理器内部进行高速处理.SDRAM 的总线由外部PLL驱动设备控制,在133MHz的最佳状态运行,SDRAM的刷新由DM642自动控制.

2.4.2 程序存储器模块(FLASH) 系统中可执行程序代码远远超过了lk bytes,故采用外扩的程序存储器,使其能够有足够的空间保存可执行程序代码.该系统中扩展了一块8M×8bit的FLASH 芯片AM29LV033C,用于存储系统程序代码,地址空间映射在 DM642的CE1空间的低位.我们采用分页的方式来访问存储器,将FLASH的高三位作为页选择位,如图4所示.这样把FLASH共分为8页,每页为1M存储空间,由DM642通过对逻辑器件FPGA 编程完成对每一页存储空间的选择.

本系统中采用从片外FLASH引导的方式加载程序,片上引导机制总是从第0页开始引导,系统的 BootLoader程序都固化在这一页.所有8个页面均映射到DM642的相同的地址空间0x90000000~ Ox9OOfffff.对FLASH寻址操作时,由DM642将EMIF提供的FLASH相对地址0x00000~Oxfffff,与 FPGA提供的页地址相加,得到数据的实际存储地址,从而实现对8M存储空间的访问.

2.5 外围通讯模块

外围通讯模块主要用于与上位机通讯.系统对检测标记图像进行实时处理后,得出导带运行情况,并将数据通过此模块反馈给上位机.系统采用标准的RS232串口作为通讯端口.通讯模块中用UTAR芯片 TL16C752B将来自DM642或SDRAM 的并行数据信号转换为串行输出,并将输入串行数据转换为并行数据.串行输出的数据再经过一个电平转换芯片MAX3243将信号的电平转换为标准的RS232串行数据格式,输入到串行通讯接口和上位机进行通讯.异步串行芯片TLI6C752B与DM642的EMIF相连,DSP 通过地址译码可以访问芯片的各个控制寄存器.

2.6 电源模块

由于系统中的器件需要几种不同的供电电压,如DM642内核电压为1.4V,DM642外部I/0口为 3.3V,外围器件为5V.电源模块采用了两片电源芯片TPS54310完成由5V到3.3V和1.4V的转换,3.3 V和1.4V电源之间连接肖特基二极管,保证DM642的内核和外部端口同时供电.整个系统中用到很多高速器件,需要高精度的供电以保证系统正常工作,因此在设计中采用模块化设计,将电源部分独立出来.有些部分如FPGA芯片和视频输入输出甚至采用单独供电,以保证给系统各部分提供稳定可靠的电源.

3 结束语

本系统采用以DSP为核心处理器,采用图像处理技术为核心技术;实现了对平网印机对花的自动检测,提出了一种将闭环控制方式应用到平网印花机对花的方法.该系统具有深入开发的扩展性,为进一步改进平网印花机自动控制系统和扩展该领域中机器视觉的应用提供了开发基础和解决方法.

来源 李鹏飞,李 鹏,张 蕾,林成荫 来源互联网

该文章暂时没有评论!

最新技术文章

点击排行